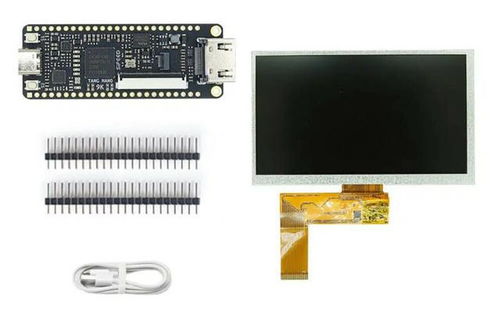

Tang Nano 9K FPGA開(kāi)發(fā)板 構(gòu)建全集成PicoRV32 RISC-V軟核系統(tǒng)的理想平臺(tái)

Tang Nano 9K是一款基于高云半導(dǎo)體小蜜蜂系列GW1NR-LV9 FPGA芯片的高性價(jià)比、入門級(jí)開(kāi)發(fā)板。其豐富的邏輯資源(約8640個(gè)LUT4)、嵌入式塊狀RAM(B-SRAM)和靈活的I/O,使其成為在單芯片上實(shí)現(xiàn)并運(yùn)行完整PicoRV32 RISC-V軟核及其外圍硬件系統(tǒng)的絕佳選擇。

一、核心優(yōu)勢(shì):為何選擇Tang Nano 9K?

- 充足的邏輯資源:GW1NR-LV9 FPGA提供了足夠的可編程邏輯單元,能夠輕松容納PicoRV32這樣的精簡(jiǎn)RISC-V內(nèi)核(通常僅需1000-2000個(gè)LUTs),并為后續(xù)擴(kuò)展復(fù)雜的自定義外設(shè)或加速器預(yù)留了廣闊空間。

- 集成存儲(chǔ)與PLL:板載的嵌入式存儲(chǔ)塊可用于實(shí)現(xiàn)軟核的指令與數(shù)據(jù)存儲(chǔ)器(如RAM或ROM),而片內(nèi)鎖相環(huán)(PLL)則能生成系統(tǒng)所需的各種時(shí)鐘頻率,確保了系統(tǒng)的高效與穩(wěn)定運(yùn)行。

- 豐富的外設(shè)接口:開(kāi)發(fā)板自帶RGB LED、按鍵、用戶IO擴(kuò)展接口、SPI Flash(用于存儲(chǔ)FPGA配置文件和軟核程序)等,為連接和模擬各類外設(shè)提供了硬件基礎(chǔ)。

二、系統(tǒng)設(shè)計(jì):模擬PicoRV32軟核與完整外設(shè)生態(tài)

在Tang Nano 9K上構(gòu)建一個(gè)完整的微處理器系統(tǒng),通常包含以下核心模塊,全部通過(guò)硬件描述語(yǔ)言(如Verilog)設(shè)計(jì)并集成:

- PicoRV32 RISC-V CPU軟核:作為系統(tǒng)的中央處理器。這是一個(gè)高度可配置、最小化的32位RISC-V實(shí)現(xiàn),支持RV32IMC指令集。設(shè)計(jì)時(shí)需將其作為一個(gè)模塊實(shí)例化,并連接至系統(tǒng)總線。

- 片上存儲(chǔ)器系統(tǒng):

- 指令存儲(chǔ)器(IMEM):通常使用FPGA的塊RAM實(shí)現(xiàn),用于存儲(chǔ)CPU執(zhí)行的程序代碼。

- 數(shù)據(jù)存儲(chǔ)器(DMEM):同樣使用塊RAM,作為CPU運(yùn)行時(shí)的工作RAM。

- 內(nèi)存映射:設(shè)計(jì)一個(gè)地址解碼器,為不同的外設(shè)(如UART、GPIO、定時(shí)器)分配唯一的地址空間。

- 系統(tǒng)總線:通常采用簡(jiǎn)單的Wishbone或AXI4-Lite等總線協(xié)議,作為CPU與所有外設(shè)之間通信的標(biāo)準(zhǔn)化通道,實(shí)現(xiàn)模塊化的設(shè)計(jì)。

- 關(guān)鍵外設(shè)IP核(硬件設(shè)計(jì)):

- 通用異步收發(fā)器(UART):用于與PC進(jìn)行串行通信,是調(diào)試和輸入輸出的關(guān)鍵。

- 通用輸入輸出(GPIO):控制板載LED、讀取按鍵狀態(tài),并連接外部擴(kuò)展設(shè)備。

- 系統(tǒng)定時(shí)器(Timer):提供精確的時(shí)間基準(zhǔn),用于任務(wù)調(diào)度、延時(shí)等。

- SPI控制器:用于讀寫(xiě)板載SPI Flash,可以實(shí)現(xiàn)“程序存儲(chǔ)于Flash、上電后加載至RAM運(yùn)行”的典型嵌入式工作流程。

- 脈沖寬度調(diào)制(PWM):可用于控制LED亮度或電機(jī)速度。

三、開(kāi)發(fā)流程與工具鏈

- 硬件設(shè)計(jì)與綜合:使用高云云源軟件(Gowin EDA)進(jìn)行Verilog編碼、綜合、布局布線和生成比特流文件。將PicoRV32源碼與自編寫(xiě)的外設(shè)模塊一同集成到頂層設(shè)計(jì)中。

- 軟件程序開(kāi)發(fā):利用RISC-V GNU工具鏈(如riscv-gcc)編寫(xiě)C/C++應(yīng)用程序。通過(guò)鏈接腳本,將程序代碼定位到設(shè)計(jì)好的存儲(chǔ)器地址空間中。

- 系統(tǒng)集成與調(diào)試:

- 將編譯好的軟件程序(.bin或.hex文件)初始化到FPGA設(shè)計(jì)中的ROM/BRAM里,或通過(guò)UART引導(dǎo)加載。

- 通過(guò)Gowin EDA的邏輯分析儀工具進(jìn)行內(nèi)部信號(hào)抓取調(diào)試。

- 最終將完整的比特流文件下載到Tang Nano 9K的SPI Flash中,實(shí)現(xiàn)上電自啟動(dòng)運(yùn)行。

四、應(yīng)用與展望

成功在Tang Nano 9K上運(yùn)行PicoRV32及全套外設(shè),標(biāo)志著一個(gè)真正意義上的片上系統(tǒng)(SoC)的實(shí)現(xiàn)。開(kāi)發(fā)者可以在此基礎(chǔ)上:

- 深入學(xué)習(xí)計(jì)算機(jī)體系結(jié)構(gòu):理解CPU、總線、存儲(chǔ)與外設(shè)如何協(xié)同工作。

- 進(jìn)行嵌入式開(kāi)發(fā)實(shí)踐:編寫(xiě)驅(qū)動(dòng)程序,控制各種硬件。

- 實(shí)現(xiàn)定制化加速:利用富余的FPGA資源,為PicoRV32添加專用的硬件加速引擎(如算法加速器),探索軟硬件協(xié)同設(shè)計(jì)的魅力。

Tang Nano 9K以其親民的價(jià)格和恰到好處的資源,為FPGA和RISC-V愛(ài)好者提供了一個(gè)從零開(kāi)始搭建并理解一個(gè)完整、可實(shí)際運(yùn)行的計(jì)算系統(tǒng)的完美沙盒。通過(guò)將PicoRV32軟核與所有必需的外設(shè)硬件集成于一體,開(kāi)發(fā)者能夠獲得從底層硬件到上層軟件的端到端設(shè)計(jì)體驗(yàn)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.calciumchloride.cn/product/59.html

更新時(shí)間:2026-04-24 03:27:43